# 微电子技术中的薄膜应用

## 1.1 引言

分层薄膜结构常应用于微电子、光电器件、平板显示器和电子封装技术中,以下列举一些典型例子。计算机上的超大规模集成电路芯片由多层薄金属膜互连组成,形成了亚微米宽的线路和通孔。半导体晶体管器件依赖于在半导体衬底上生长的外延薄膜,例如在 n<sup>+</sup>型 Si 衬底上生长 p 型 Si 薄层<sup>[1-3]</sup>。晶体管器件的绝缘栅极由半导体上生长的氧化物薄层形成。固态激光器是将发光半导体薄膜夹在不同半导体薄膜之间。在电子和光学系统中,有源元器件通常位于表面上方几微米内,而这一尺度就是薄膜技术可以应用的范围。薄膜填补了单层(或纳米级结构)和块体结构之间的尺度范围。其厚度从几纳米到几微米。本书探讨了薄膜加工和薄膜可靠性中的科学问题,以及它们在电子技术和器件中的应用<sup>[4]</sup>。本章首先通过示例介绍薄膜在现代先进技术中的应用。

# 1.2 金属氧化物半导体场效应晶体管

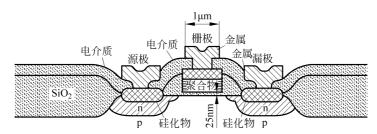

薄膜技术的进步对集成电路和光电子学的演进至关重要。当下,我们可以在一片指甲大小的硅片上制造数亿个晶体管。这些晶体管必须通过薄膜线路相互连接,以形成电路一起工作。存储器件中的基本电路非常简单,由一个晶体管和一个电容器组成。如图 1.1 所示为场效应晶体管的剖面示意图,它包括一个 n<sup>+</sup>/p/n<sup>+</sup>型的晶体管和一个覆盖在 p 型沟道上的薄栅氧化物栅极。栅极是一个双层结构,

包括 Si 和金属组成的硅化物和重掺杂多晶硅。晶体管中的 n<sup>+</sup> 区域是源极和漏极 区域,并通过硅化物接触连接到字线。因此,硅化物既用作栅极接触也用作源极和漏极接触。有一条字线将源极接触连接到电容器。

图 1.1 n<sup>+</sup>/p/n<sup>+</sup>型场效应晶体管的剖面示意图,包括一个具有 p 型沟道上薄栅氧化物的栅极

电容器作为一种存储单元,可以存储"1"(电容器充满电荷时)或"0"(电容器为空或不存储电荷时)。金属氧化物半导体(MOS)场效应晶体管(FET)作为控制器(或栅极)允许电容器放电或不放电,以便我们读取或检测电容器的两种状态,即充满或空置[1-3]。

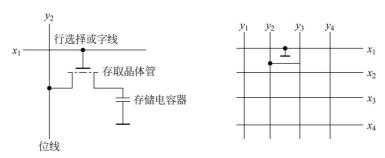

图 1.2 描绘了一个 MOSFET 的二维集成电路阵列。在 x 坐标上,有  $x_1$ , $x_2$ , $x_3$ , $x_4$  等;而在 y 坐标上,有  $y_1$ , $y_2$ , $y_3$ , $y_4$  等。在每个坐标点(x,y)处,例如取 ( $x_1$ , $y_2$ ),构建一个由 MOSFET 和电容器组成的存储单元。为了启动存储单元,需要从字线向栅极施加一个开启电压。它将吸引电子到 p 区域,并在栅极氧化物下形成一个反型层。带有电子的反型层实现了两个  $n^+$  区域的电导通。如果电容器充满了存储的电荷,将放电,以便在位线末端检测到信号脉冲。此时,将在点( $x_1$ , $y_2$ )上识别出一个存储位"1"的存储单元。另外,如果电容器没有存储电荷,栅极触发时将不会放电,并且不会检测到任何信号。那么,在点( $x_1$ , $y_2$ )上将有一个存储位"0"的存储单元。如图 1.2 所示的二维集成电路能够操作和检测电路的

图 1.2 MOSFET 的二维集成电路阵列示意图 图片来源: VLSI Technology, S. M. Sze(1988),第 494 页。已获使用许可

每个存储单元,因此这样的电路阵列被称为随机存取存储器(RAM)。由于电容器与线路相互连接,所以电容器会漏电,电容保存电荷的时间有限,通常使用动态随机存取存储器(DRAM)来设计该器件,即必须定时对电容充电,而这种补充电荷是一个动态过程,称为刷新。在某些器件中,当栅极被隔离时,可以将其用作浮置栅极。

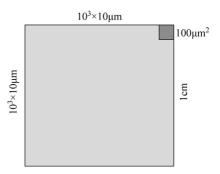

图 1.3 描述了一个尺寸为  $1 \text{cm} \times 1 \text{cm}$  的硅芯片,将其分成了  $10^3 \times 10^3 = 10^6$  个小正方形,使每个小正方形的面积为  $10 \mu \text{m} \times 10 \mu \text{m}$ 。在每个小正方形或单元区域中,如果能够制造一个 MOSFET 和一个电容器,就制造了一个拥有 100 万个存储单元的芯片。更不必讲,我们能够通过它们的位线和字线进行互连。此外,使用该芯片时,只要将其连接到外部电路进行控制即可,这是电子封装技术的一个功能。

图 1.3 一个尺寸为 1cm×1cm 的 硅芯片的示意图

接下来,将  $10\mu m \times 10\mu m$  的面积分成 4 个更小的区域,即大约  $5\mu m \times 5\mu m$  的单元

4 个更小的区域,即大约  $5\mu m \times 5\mu m$  的单元格。如果可以在较小的区域内缩小并构建一个 MOSFET 和一个电容器,那么将拥有一个具有 400 万个存储单元的芯片。这是硅微电子行业在过去 25 年中微型化的原则,或者说是摩尔定律所表明的递增趋势。一个技术代的进步意味着芯片电路密度的增加因子是 4,从 1、4、16、64、256 到 1024 等。该行业在 20 世纪 60 年代末从大约 1000 个存储单元开始,已发展到今天的约十亿个存储单元。表 1. 1 列出了几代器件中单元格的尺寸变化。随着单元格尺寸变小,单元格中的晶体管、电容器和互连元素的特征尺寸也相应变小。单元尺寸缩小的背后有一条缩放定律,影响着晶体管以及互连的电气特性。

| 单元密度             | 光刻线宽/μm   | 单元面积/μm² |

|------------------|-----------|----------|

| 1Mb              | 1         | 33       |

| $4\mathrm{Mb}$   | 0.7       | 11       |

| $16\mathrm{Mb}$  | 0.5       | 4.5      |

| $64\mathrm{Mb}$  | 0.35(深紫外) | 1.5      |

| $256\mathrm{Mb}$ | 0.25(X射线) | 0.5      |

| 1Gb              | 0.18      | 0.15     |

表 1.1 不同技术代器件中单元多维指标变化

通过使用 Al 或 Cu 薄膜多层互连将所有晶体管连接在一起,实现了超大规模集成电路(VLSI)。多层薄膜互连结构的工艺和可靠性对于器件制造设计至关重

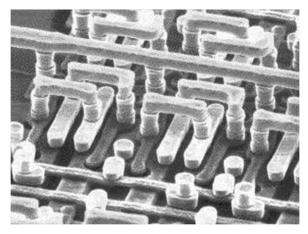

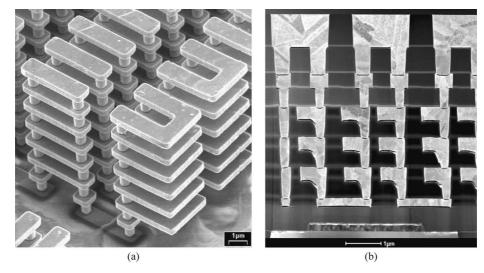

要。如今,晶体管上建立了 8 层或更多层的互连。图 1.4 显示了 Si 表面上去除绝缘介质后的两层 Al 互连的扫描电子显微镜(SEM)图像。Al 线的宽度为 0.5 μm,它们之间的间距为 0.5 μm,因此线宽为 1 μm。如果在 1 cm×1 cm 的区域内,我们可以拥有 10<sup>4</sup> 条线,每条线的长度为 1 cm,那么在这样的一层中互连的总长度为 100 m。当我们在指甲大小的芯片上构建 8 层这样的结构时,总互连长度超过 1 km。图 1.5(a)显示了一个 8 层 Cu 互连结构的 SEM 图像(在层间介质材料被刻蚀后拍摄)。图 1.5(b)显示了在 Si 表面构建的 6 层 Cu 互连结构的横截面透射电子显微镜(TEM)图像。这里,最窄互连通孔的宽度为 0.25 μm。层间通孔之间的对准是器件制造中一个具有挑战性的问题。

图 1.4 这是一张 SEM 图像,显示了去除绝缘介质后 Si 表面上的两层 Al 互连。 Al 线的宽度为 0.5 μm,线间距也为 0.5 μm,因此线宽为 1 μm

制作层状金属化结构的生产成本现在已经超过了整个硅晶圆生产成本的一半。在互连金属化中,C-54 TiSi<sub>2</sub>、CoSi<sub>2</sub> 或 NiSi 的硅化物已经被用作场效应晶体管的栅极、源极和漏极的接触材料。在 Al 互连技术中,W 被用作互层通孔。在 Cu 互连技术中,它也被用作第一层的通孔。为了在互连技术中使用 Cu,Cu 必须镀覆在用 Ta 或 TiN 制造、非常薄的附着和扩散阻挡层上。这些薄膜的加工、性质和可靠性与工艺的进步密切相关。

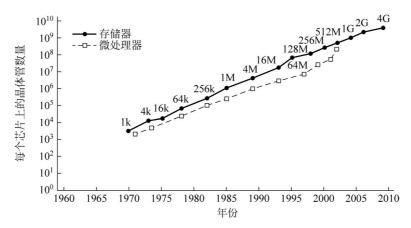

显然,如果一个单元的尺寸是  $1\mu m \times 1\mu m$ ,那么它的电路元件必须小于  $1\mu m$ 。在微型化趋势下,不仅横向尺寸将变小,垂直尺寸(如栅极氧化物厚度)也必须减薄。毫无疑问,不能通过不断缩小尺寸制造越来越小的器件。摩尔定律描述了微型化趋势或器件尺寸缩小的进展,即芯片上的电路密度将每 18 个月翻一倍。图 1.6 显示了集成电路中的存储器和逻辑单元电路的密度随时间变化的示意曲线。它是一个对数关系线性图,遵循摩尔定律。

图 1.5 (a) 显示了 8 层 Cu 互连结构的 SEM 图像,该图像为在层间介电材料被蚀刻掉后拍摄; (b) 显示了在 Si 表面上建造的 6 层 Cu 互连结构的横截面 TEM 图像。这里,最窄互连通孔的宽度为 0.25 μm

图 1.6 显示了集成电路中的存储器和逻辑单元电路的密度随时间的变化。这是一个对数关系线性图,遵循摩尔定律

#### 1.2.1 自对准硅化物接触和栅极

上述 MOSFET 器件中的关键尺寸是栅极宽或源漏极之间的距离,称为器件的特征尺寸。现今,特征尺寸已缩小到纳米级别,最小可达 45nm,预计不久将会达到 33nm 甚至更小。在制造过程中,如果栅极和触点是由不同材料制成的,则这一特征尺寸需要两个不同的工艺步骤或两个光刻步骤来实现,因此需要高精度对准,

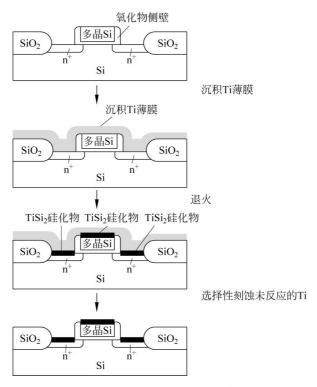

然而在纳米尺度上控制特征尺寸是十分困难的。为了克服这一关键步骤,发明了自对准硅化物(salicide)工艺。图 1.7显示了自对准硅化物工艺的示意图。栅极和源极/漏极接触都由 C-54 TiSi<sub>2</sub> 制成。在栅极氧化物上方是一层高掺杂的多晶硅层,在源极/漏极接触区域上方是一层高掺杂的单晶 n<sup>+</sup> Si 层,其间由两个 SiO<sub>2</sub> 侧壁分开。侧壁之间的间距和侧壁的厚度确定了特征尺寸的横向尺寸。当沉积和退火一层薄的 Ti 膜时,C-54 TiSi<sub>2</sub> 会同时形成在栅极接触和源极/漏极接触上。但是在侧壁氧化物上的 Ti 不会与氧化物反应形成硅化物,可以选择性地蚀刻未反应的 Ti,从而可以在一个光刻步骤中实现栅极和接触之间的电隔离。这种自对准硅化物工艺避免了高精度对准问题,并实现了栅极和触点的自对准工艺。

图 1.7 自对准硅化物工艺示意图

在薄膜领域的文献中,有许多关于通过薄金属膜与硅反应形成硅化物的论述。由于一个硅芯片上有数亿个硅化物接触和栅极,它们应该具有相同的微观结构和电性能,因此控制硅化物的形成一直是 VLSI 器件制造中非常重要的工艺步骤。硅化物形成的动力学将在第8章介绍。

#### 倒装焊中的薄膜下凸点金属化 1.3

将芯片上的 VLSI 可靠连接到外部电路,是电子封装技术的主要功能[5-6]。为 了给所有这些芯片上的互连线提供外部电气引脚,可能需要在中央处理器芯片表 面使用数千个输入/输出(I/O)电气触点。目前,提供这种高密度芯片表面 I/O 触 点的唯一实用和可靠的方法是使用微小焊球的面积阵列。可以使用直径为 50μm、 间距为 50μm 的焊球,因此节距为 100μm。将 100 个焊球放置在 1cm 长度上,或将 10000 个焊球放置在 1cm<sup>2</sup> 的区域上。目前使用的焊球直径通常约为 100μm,电子 封装行业中焊球工艺称为凸点技术。由于使用了如此小规格和大量的焊球,自 1999 年以来,国际半导体技术路线图(ITRS)已经将倒装焊技术中的焊接接点确定 为一个重要的研究课题,涉及其在制造中的量产和在应用中的可靠性。

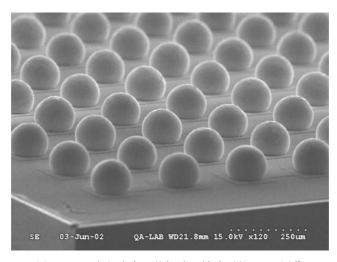

什么是倒装焊技术?它是一种通过焊点提供大量电气连接的技术,用于芯片 和封装基板之间。芯片倒装,使其面向下,让高集成度的电路面向基板。通过芯片 和其基板之间的一系列焊盘实现电连接。图 1.8 展示了芯片表面的一组焊球区域 阵列。为了将芯片连接到基板上,将芯片倒装过来,使芯片的 VLSI 一侧朝下,面 向基板。

图 1.8 一个芯片表面的锡球区域阵列的 SEM 图像

倒装焊技术用于制造大型计算机已超半个世纪。它起源于 20 世纪 60 年代在 陶瓷模块上封装芯片的可控塌陷芯片连接或 C-4 技术。一般来说,倒装焊技术的 优点包括更小的封装尺寸、更多的 I/O 引脚数量以及更高的性能与可靠性。现在 它在芯片封装等消费类产品中得到广泛应用,封装基板的尺寸几乎与芯片相同。在手持设备中需要小的封装尺寸,其中形状因子非常重要。在手持终端或计算机中,对更高性能和更强大的功能需求将需要大量的电气 I/O 引脚。更高的芯片性能,是因为芯片中央的焊料球使器件可以在较低电压和更高速度下工作。此外,倒装焊技术是目前唯一可以实现所需可靠性的技术。后面的章节将讨论与电迁移和应力迁移等相关的可靠性问题。

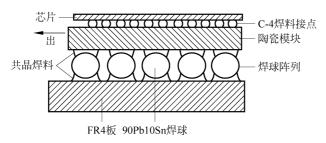

在最初开发 VLSI 芯片技术时,需要高密度的布线和互连的封装技术。这促成了主要用于计算机主机的多层金属-陶瓷模块和多芯片模块的发展。在多层金属-陶瓷模块中,多层 Mo 线被埋入陶瓷基板中。每个模块最多可安装 100 个 Si 芯片。几个这样的陶瓷模块被连接到一个大型的印刷电路板上,形成了如图 1.9 所示的计算机主机的两级封装方案。它由芯片到陶瓷模块的第一级封装和陶瓷模块到聚合物印刷电路板的第二级封装组成。

图 1.9 计算机主机的两级封装方案示意图。它包括芯片到陶瓷模块的第一级封装和陶瓷模块到聚合物印刷电路板的第二级封装

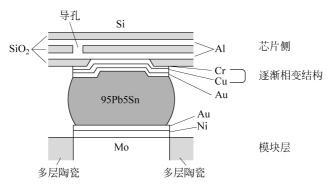

图 1.10 展示了第一级倒装 C-4 焊点的剖面示意图。在第一级封装中,芯片侧的下置金属层(UBM)由 Cr/Cu/Au 三层薄膜组成。实际上,Cr/Cu 层具有相变的微观结构,其作用是提高 Cr 和 Cu 之间的附着力,并增强其抗锡反应的能力。锡反应可能会溶出 Cu,因此相变的 Cr/Cu 由 Cr 和 Cu 的共沉积形成,使之具有成分梯度,可以在多次锡反应中持续存在。回流意味着焊料经历了略高于其熔点的温度,使其熔化。在熔融状态下,焊料会与 Cu 反应,形成金属键或焊点中的金属间化合物(IMC)。在连接处的基板侧,陶瓷表面的金属焊盘材料通常是 Ni/Au。连接UBM 和焊盘的焊料是高铅合金,如 95Pb5Sn 或 97Pb3Sn。

最初,芯片上的焊料凸点是通过蒸发沉积并使用剥离法进行布图的,后来通过选择性电镀沉积。最近,在一种新的 C-4 工艺中,使用模板形成二维焊球阵列,然后将具有接收 UBM 阵列的芯片放置在模板上,以便在回流中将所有焊球转移到芯片上,在焊球与 UBM 间发生反应。新工艺的优点是在选择性电镀沉积中不需要厚的光刻胶,并且模板可以重复使用以降低成本。

图 1.10 倒装芯片焊点的剖面示意图

在选择性电镀沉积 C-4 工艺中,去除用于电镀的光刻胶和电线后,芯片表面上会留下一列圆柱形的焊锡柱或凸点。高铅焊料的熔点超过 300℃。在第一次热回流(约 350℃)中,列状的焊锡柱会变成球状凸点,覆盖在 UBM 上。由于 SiO₂表面不能被熔融的焊料浸润,熔融的焊锡凸点的底部由 UBM 的大小确定,因此熔融的焊锡凸点会在 UBM 接触处升起或凸起。UBM 接触控制着给定体积的焊锡球的尺寸(高度和直径)。通常,UBM 接触被称为焊球受限金属化(BLM)。由于 BLM控制了焊锡球熔化时固定体积的高度,这就是"可控"一词在"可控塌陷芯片连接"中的含义。如果没有控制,焊锡球会在 UBM 上扩散,芯片和模块之间的间隙就太小了。

将一组焊球的芯片连接到陶瓷模块上,需要使用第二次回流。在第二次回流 过程中,熔化的焊球表面能通过自对准力将芯片在模块上自动定位。当焊料熔化 以将芯片连接到模块时,芯片会稍微下降和旋转。这种下降和旋转是由于熔化焊 球的表面张力减小造成的,这实现了芯片和模块之间的对准,因此这是一个受控塌 陷过程,叫作 collapse,意思是,当焊球的区域阵列熔化并浸湿模块上的焊盘时,芯 片会稍微下降和旋转。

高铅焊料是一种高熔点的焊料,但芯片和陶瓷模块都能够承受高温回流而无损。此外,高铅焊料与铜发生反应形成层状的 Cu<sub>3</sub> Sn,可以在多次回流过程中持续使用而不失效。值得注意的是,Cr/Cu/Au 三层金属膜中的每种金属都是因特定原因而选择的。首先,焊料不能与铝线相互浸润,所以选择 Cu,因为 Cu 与 Sn 反应形成 IMC 可以实现金属接点。其次,Cu 不能很好地附着在 SiO<sub>2</sub> 的介电表面,因此选择 Cr 作为 Cu 附着在 SiO<sub>2</sub> 上的黏合层。逐渐相变 Cu/Cr UBM 的研制旨在提高 Cu 与 Cr 之间的附着力。由于 Cr 和 Cu 是不相溶的,当它们共沉积时,其晶粒形成相互锁定的微观结构。在这样的逐渐相变结构中,Cu 更好地附着于 Cr,Cu 在回流过程中被溶出,与 Sn 反应形成 IMC 也就更难。此外,逐渐相变结构提

供了 IMC 的机械锁定。最后,Au 被用作表面钝化涂层,以防止 Cu 的氧化或腐蚀,并且作为增强焊料浸润的表面处理。已有文献对 Cr/Cu 和 Cu/Au 双层薄膜中的 互扩散和反应进行了大量研究。

再将陶瓷模块与聚合物印刷电路板进行二级封装,即把陶瓷基板焊接到聚合物印刷电路板上,另一组区域阵列的焊球被放置在陶瓷基板的背面。它们合称为焊球阵列(BGA),每个焊球的直径比 C-4 焊球大得多。通常 BGA 焊球的直径约为760 $\mu$ m。它们是共晶 SnPb 焊料,熔点(183 $^{\circ}$ )较低,可在 220 $^{\circ}$  左右进行回流焊接。有时也会使用高(熔点)Pb 和共晶 SnPb 的复合焊球,焊球核心是高 Pb 的。显然,在这种共晶焊料的第三次回流中,第一级封装中的高 Pb 焊点或复合焊球中的高 Pb 核心不会熔化。在某些应用中,复合焊球中的高 Pb 核心可以被 Cu 球所替代。

鉴于对铅污染环境的担忧日益加剧,美国国会有四项反铅议案正在等待通过,其中一项来自环境保护局。欧盟于 2006 年 7 月 1 日发布了一项指令,要求在所有电子消费品中禁止使用含铅焊料。虽然汽车电池在工业应用中使用了高达 88%的铅,而电子设备只使用了 1%的铅,但消费电子垃圾是地下水铅污染 20%~30%的来源。这就是推出禁令的原因。

目前还没有发现可以取代 Pb,并在焊接接点中能够很好地发挥作用的化学元素。最有前途的无铅焊料是共晶 SnAgCu、共晶 SnAg 和共晶 SnCu,用来取代共晶 SnPb。这些基于 Sn 的焊料具有非常高的 Sn 浓度,例如共晶 SnCu 具有 99.3% (质量分数)的 Sn,而共晶 SnAgCu 具有质量分数为 95%~96%的 Sn。这些无铅焊料中非常高的 Sn 浓度导致了 Cu-Sn 反应的高速率,进而导致上述的薄膜 Cr/Cu/Au UBM 中的可靠性问题。迄今为止,还没有适合无铅焊接的薄膜 UBM,特别是在考虑对抗电迁移的可靠性方面。

### 1.4 计算机为什么很少出现可靠性故障

上面已经提到,电迁移是一个严重的可靠性问题。然而,很少听说计算机因为电迁移而失效。这是因为电子工业很早就认识到了这个问题,并花费了很多精力进行研究。通过在一定加速测试条件下测量计算机的平均无故障时间(MTTF),可以预测计算机在正常使用中的寿命。可靠性在设计阶段就已经考虑到了,因此已经规定计算机的工作条件,如施加的电流密度和温度。因此,在正常使用时不会遇到计算机故障的问题。